Zhengmao Li som är chef för China Mobile, världens största mobiloperatör, förklarade vid årets mobilmässa i Barcelona att 5G kommer att kräva tre gånger fler basstationer för att ge samma täckning som LTE, samt konsumera tre gånger mer effekt och kosta fyra gånger mer än LTE.

Zhengmao Li som är chef för China Mobile, världens största mobiloperatör, förklarade vid årets mobilmässa i Barcelona att 5G kommer att kräva tre gånger fler basstationer för att ge samma täckning som LTE, samt konsumera tre gånger mer effekt och kosta fyra gånger mer än LTE.

Ladda ner artikeln här (länk, pdf). Fler tekniska rapporter finns på etn.se/expert |

Dessa tankar om kostnad och effekt innebär helt klart att det blir svårare att försvara den traditionella 3G/4G-lösningen där mobilinfrastrukturen baseras på FPGA- och DSP-kretsar. Tillverkarna av mobilutrustning inriktar sig nu mot asicar för att balansera kompromisserna mellan den korta räckvidden med millimetervågor, standardens låga latens, dess höga genomströmning och användandet av massiv Mimo med flera antenner vilket gör det möjligt att kommunicera på millimetervågsområdet utan att handen dämpar signalen.

Kompromissen mellan FPGA, DSP och asic

FPGA:er ger stor flexibilitet samtidigt som de fördelar utvecklingskostnaderna över en mycket stor mängd användare. De minskar också arbetsinsatsen för att utveckla den firmware som krävs för att konfigurera dem. Men detta kommer till kostnaden av en ineffektiv användning av kiselytan, hög effektförbrukning och försämrad klockprestanda. Visserligen har den nya generationen av SoC-FPGA:er de prestanda som krävs för många av de digitala komponenterna i 5G. Men de uppfyller inte alltid kraven på låg effekt och låga kostnader. Ibland har de inte den nödvändiga logiken eller möjligheterna att ha minne på chipet.

Att istället använda en DSP-baserad lösning, från exempelvis Tensilica eller Ceva, är en möjlighet. Men även om en sådan lösning fortfarande ger flexibilitet så kräver den avsevärd bearbetningskraft och högre effektförbrukning jämfört med hårdvarulogiken hos en asic.

Övergången till asicar är ett steg tillbaka för infrastruktursektorn, men den är en fortsättning på en trend. Asicar för AI och självkörande fordon har på senare tid fått stora rubriker med nyheter från Tesla, Facebook, Amazon och Google. Och asicar är vanligt förekommande i lågkostnadsapplikationer som IoT, i medicinska apparater och i fordonsstyrsystem. Här ger användandet av äldre ”More than Moore”-processer möjlighet att utveckla kostnadseffektiva asic-processer som exempelvis balanserar effektförbrukning och chipstorlek men ändå gör att det går att införa finesser som RF-block och Mems-sensorer.

Migrering från en FPGA-baserad konstruktion

Att migrera från en FPGA (som Xilinx Zynq med ett RF-block) kommer kräva avsevärda NRE-kostnader.

Användandet av licenserbara IP-kärnor kommer på liknande sätt att ha stor betydelse för att reducera riskerna och kostnaderna. Den som vill veta mer om detta och få en översikt över IP för Zynq hittar mer information i den tekniska referensmanualen för Zynq UltraScale+.

Processorkärnan, liksom minnesgränssnitt och periferifunktioner finns tillgängliga från Arm, Synopsys och Cadence. Snabba seriegränssnitt (SerDes PHY:er) och dataomvandlare kan erhållas på licens från många leverantörer, däribland Synopsys, Cadence och Rambus (liksom många andra).

På samma sätt kan viktig IP licenseras från tredjepartskällor för att ersätta leverantörsspecifik FPGA-IP. Detta gäller bland annat för en mängd mjuk IP som FEC-acceleratorer, digitala nedkonverterare (DDC), digitala uppkonverterare (DUC), Singular-Value Decomposition (SVD), flyttalsenheter (FPU), Matrix Math Engines och FFT-kärnor.

Websidor som Design & Reuse gör det enklare att söka efter denna typ av IP.

Under processen att migrera en FPGA till en asic kommer asic-leverantören att hjälpa sina kunder för att se till att designreglerna följs. Det gäller exempelvis användandet av klockor, resets och kodningstyper, och att garantera anpassning till DFT (Design for Test). Andra tjänster finns vanligen också tillgängliga, som kan ta kundernas högnivå-systemmodeller och konvertera dem till effektiva hårdvaruacceleratorer som är lämpliga att använda i ett SoC.

Lägga till flexibilitet till asicar

Den viktiga fördelen med FPGA:er har alltid varit deras flexibilitet med möjligheten att uppdatera hårdvaruacceleratorer i takt med att algoritmerna förbättras. Detta har av tradition skett genom att man lägger in avancerade DSP-kärnor – från exempelvis Tensilica eller Ceva – eller fler avancerade processorkärnor från Arm (förutom de A53- och R5-kärnor som redan finns i FPGA-kretsarna). Att lägga till dessa extra Armprocessorer ger också fördelen att utvecklingen av mjukvaran förenklas.

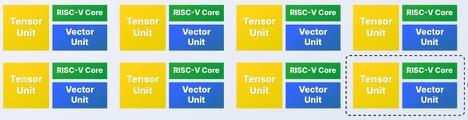

Men den nya generationen av FPGA-block som kan integreras i asicar (eFPGA) från Achronix, Flex Logix och Menta ger oss en tredje väg att uppnå flexibiliteten hos FPGA-logik i en kundanpassad asic. Dessa FPGA-block kan vanligen bara erbjuda några tusen logikelement per kvadratmillimeter kisel, så att använda dem kan motverka en del av de effekt- och kostnadsbesparingar som en asic ger. Vi rekommenderar att de används sparsamt – som en ”fribiljett ut ur fängelset”.

Införa millimetervågor

Ett av de viktigaste elementen i 5G är införandet av millimetervågsfrekvenser som ger större bandbredder. Frekvensallokeringen varierar från land till land. FCC i USA frigör till exempel de licenserade banden 28, 37 och 29 GHz (kombinerad bandbredd 3,85 GHz) samt ett 14 GHz stort olicenserat spektrum från 57 till 71 GHz.

För RF-asicar för millimetervågsområdet – från 10 GHz till 80 GHz – finns CMOS-processer från 55 nm till 22 nm som kommer att ge prestanda som passar bra för ett antal olika 5G-applikationer. De mindre noderna kan användas för att implementera de – icke oviktiga – digitala logikfunktioner som krävs för digital lobformning, integrerad basbandsbearbetning och embedded-processorkärnor.

Samtidigt kan FD-SOI (fully-depleted silicon-on-insulator) ge fördelar över vanliga CMOS-processer för denna typ av applikationer. Exempel är förbättrade brusfaktorer vid en given effektbudget, högre RF-uteffekt, bättre kanalseparation och möjligheten att skala effekt och prestanda genom metoder med Adaptive Body-Bias. Visserligen kan användandet av FD-SOI öka kostnaden, men detta kan mildras i applikationer som antenner med styrbara lober där de förbättrade brusfaktorerna och den högre effekten per krets kan medföra att det räcker med färre RF-kretsar.

Slutsats – balansera kostnaderna i 5G

5G för med sig ett antal utmaningar avseende effekt, kostnader och räckvidd. Dessa påskyndar övergången för infrastruktursektorn från de FPGA- och DSP-kretsar som används i 3G/4G-system tillbaka till asicar som är bättre lämpade.

Detta behöver inte vara något privilegium enbart för de rikaste företagen. Visst har företag som Tesla, Facebook och Google fått stora rubriker för asicprojekt som kostat många miljarder dollar. Men dessa projekt handlar om utrustning för AI och självkörande fordon, där de mest avancerade teknikerna har avgörande betydelse. 5G-utrustning behöver inte samma spjutspetsteknik.

Detta gör att kostnaderna för att använda en asicbaserad lösning kan minskas avsevärt.

Om vi exempelvis ser på kraven för 5G-utrustning kan vi uppskatta att NRE-kostnaderna (inklusive IP-licensering, utveckling och produktanpassning) för att utveckla en 16 nm FinFET-asic ligger omkring 18 miljoner dollar, med ett styckpris (baserat på chipstorlek, kapsling och testtid) på ca 6,20 dollar i volym. Motsvarande kostnad för att utveckla en 22/28 nm asic skulle uppgå till cirka 14-15 miljoner dollar, med ett styckpris på cirka 9,50 dollar.

Detta kan jämföras med en FPGA-lösning, exempelvis Xilinx UltraScale+ för kommunikationsapplikationer (som kostar 975 dollar per styck på Digi-Key), som inte skulle ha några NRE-kostnader och ett uppskattat styckpris på 100-200 dollar.

Om vi förutsätter en produktionsvolym på en miljon enheter per år (en konservativ uppskattning) skulle 16 nm FinFET-lösningen vara mest kostnadseffektiv efter bara 13 månader.

Uppenbart är att när vi går mot mer avancerade litografiprocesser, som 10 nm, så kommer det att ge en snabb ökning av NRE-kostnaderna för IP-licensering av PHY:er, ADC:er och DAC:ar plus masker. Och kostnaden skulle bli ännu högre om vi skulle använda 7 nm.

Men medan 5G-chip kräver nodstorlekar på 7 till 40 nm är det värt att notera att prestanda hos soft-logic-konstruktioner i en asic i stort sett är lika höga som hos en FPGA som är en till två noder mindre.

Rent konkret betyder det att en 22/28 nm asic skulle ge lika höga logikprestanda som en 16 nm FPGA. Det ger möjligheter att sänka både kostnaderna och effektförbrukningen i 5G-applikationer.

Till detta kommer att exakt samma IP från Arm som används i Xilinx UltraScale+ FPGA också kan användas i asic:en. Det innebär att mjukvarukompatibiliteten (och investeringarna i mjukvara) med Xilinx-kretsen bibehålls.

Så trots förlusten i flexibilitet jämfört med en FPGA utgör kostnaden och effektförbrukningen övertygande skäl till att tillverkarna av mobilutrustning skall använda asicar för att uppfylla kraven från 5G.